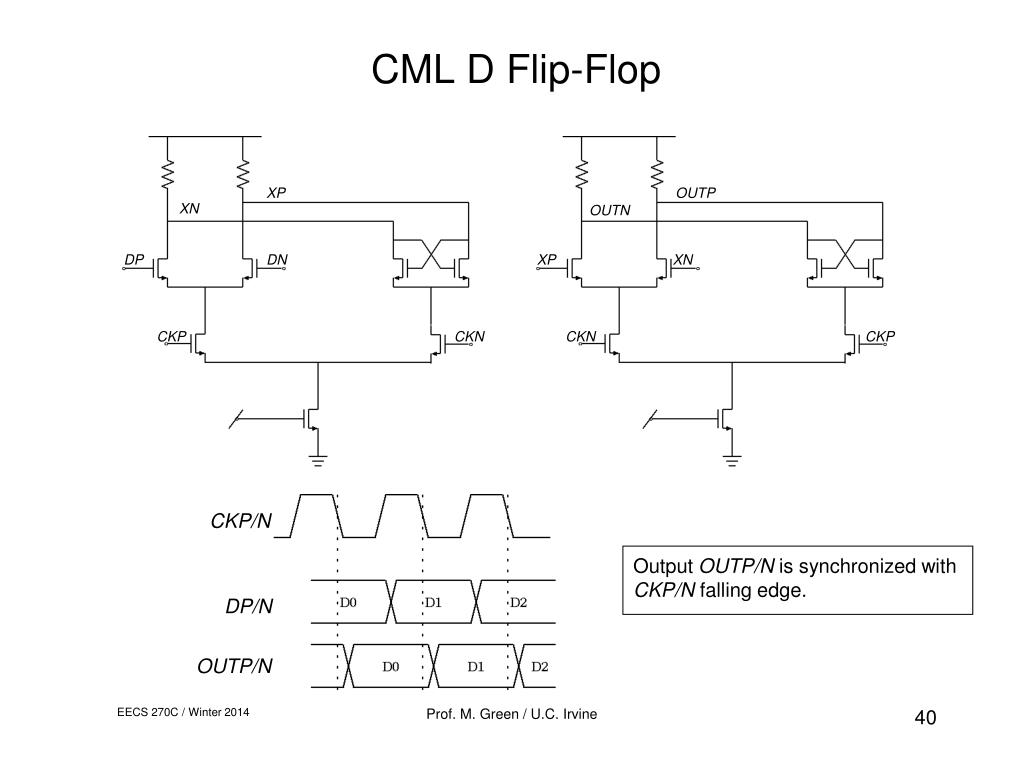

Figure 1 from High-frequency CML clock dividers in 0.13-/spl mu/m CMOS operating up to 38 GHz | Semantic Scholar

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

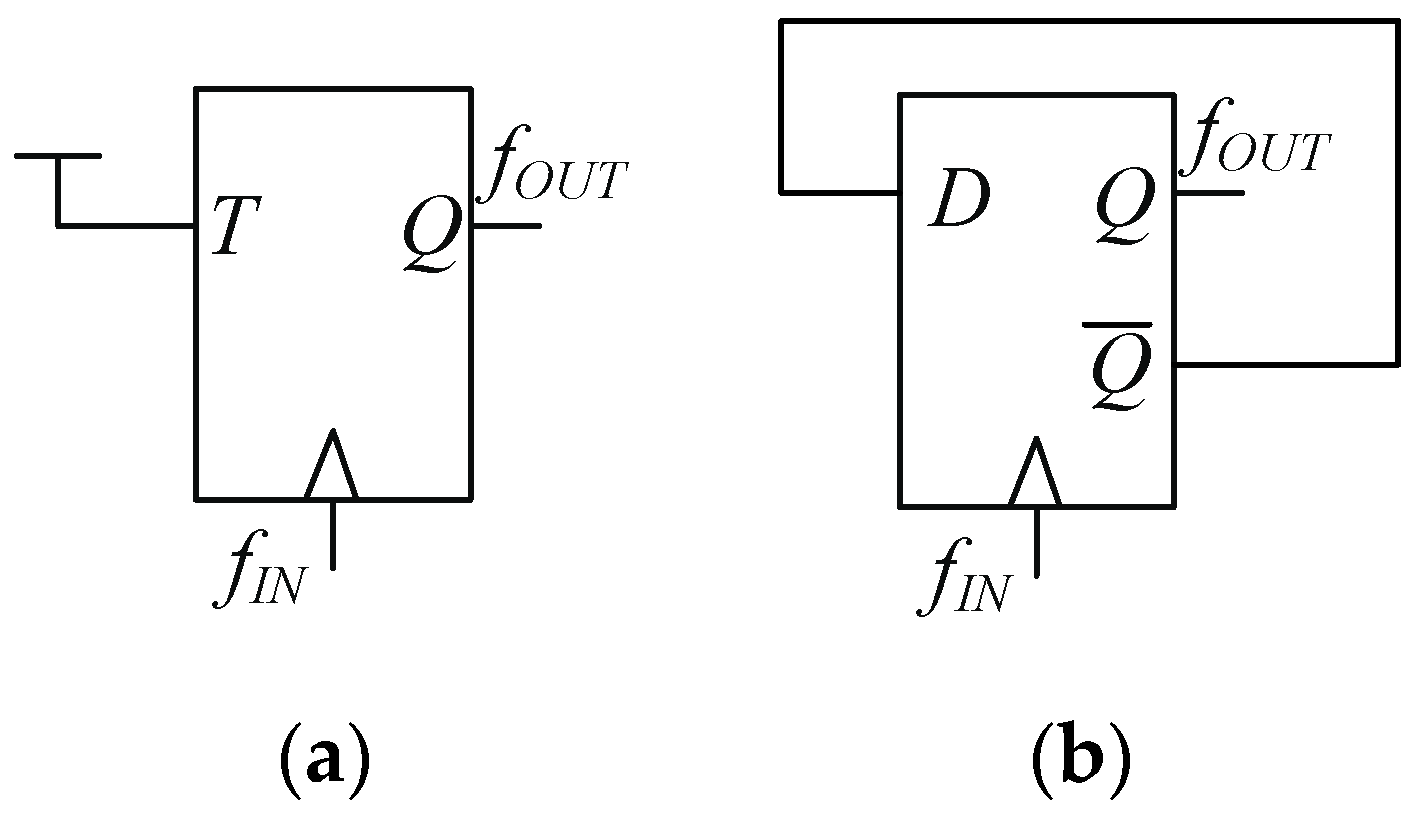

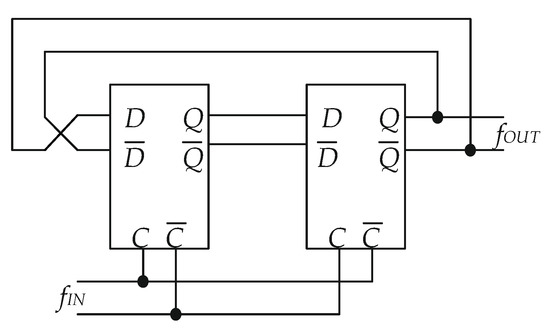

Electronics | Free Full-Text | 0.5-V Frequency Dividers in Folded MCML Exploiting Forward Body Bias: Analysis and Comparison

PDF) Low-power high-speed performance of current-mode logic D flip-flop topology using negative-differential-resistance devices

Electronics | Free Full-Text | A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS

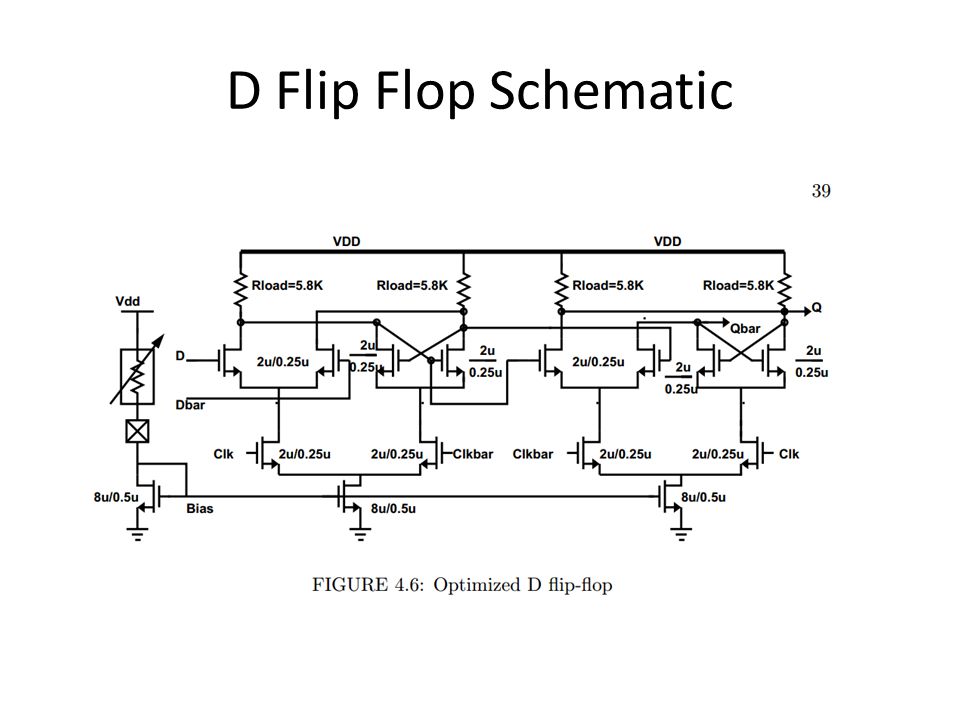

Part 01: Proposal and Overview. Dual Modulus Prescaler Using Current Mode Logic Goals 2.5 GHz Operation 8/9 Dual Modulus 0.18uM BSIM 3 Model. - ppt download

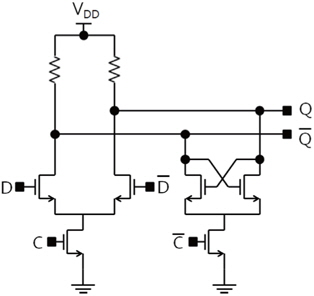

Help me calculate the device size of CML/SCL latch design and simulate the gain of it | Forum for Electronics

![PDF] New RTD-based set/reset latch IC for high-speed mobile D-flip flops | Semantic Scholar PDF] New RTD-based set/reset latch IC for high-speed mobile D-flip flops | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/a9f1b39596e7f08405b62eebe623914a1e5c78d1/2-Figure2-1.png)